#### **POWER MANAGEMENT**

### **Features**

- Input Voltage Range: 4.5V to 13.5V

- 1% Voltage Reference Accuracy

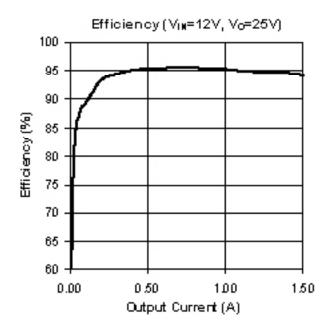

- Up to 95% Efficiency

- Input Disconnect FET Drive

- In-rush Current Control

- Internal Compensation

- **Programmable Current Limit**

- **Programmable Soft Start**

- 800mA Typical PWM Gate Drive

- 400kHz Switching Frequency

- **Under Voltage Lockout**

- <200uA Shutdown Current

- -40°C to +85°C Temperature Range

- MSOP-8 Package, Fully WEEE and RoHS Compliant

## **Applications**

- **Portable Devices**

- Flat Panel TV

- TV Set Top Box

- **Auxiliary Supplies**

- **Peripheral Card Supplies**

- **Industrial Power Supply**

- High Density DC/DC Conversion

# **Simple PWM Boost Controller** with Input Disconnect FET Drive

### **Description**

The SC2604 is a versatile, low-cost, voltage-mode PWM controller designed for boost DC/DC power supply applications. It features input disconnect FET driver allowing power source and load separation at shutdown mode, which eliminates possible leakage current from source to load. Also, it prevents catastrophic failure when output is shorted during operation.

The SC2604 also includes temperature compensated voltage reference, internal ramp, current limit comparator, internally compensated error amplifier, and floating driver with charge pump. Programmable soft start controls in-rush current and reduces output voltage overshoot. Hiccup mode over-current protection allows system autoretry and ease of trouble shooting.

Internally compensated feedback loop makes power supply design simple, and eliminates the need for external compensation network.

The SC2604 is available in MSOP-8 package with rated temperature range of -40°C to +85°C.

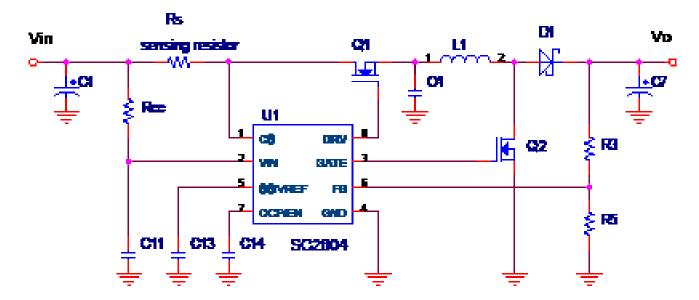

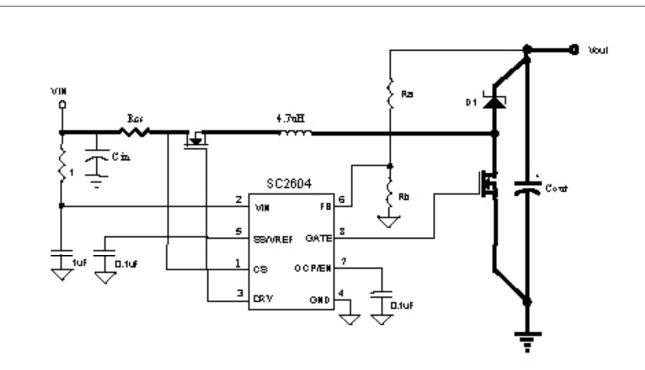

# **Typical Application Circuit**

Figure 1. 12V to 25V/1A Boost Converter with Over Current Protection

January 4, 2008 www.semtech.com 1

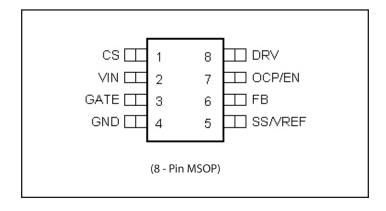

# **Pin Configuration**

# **Ordering Information**

| Device                        | Package          |

|-------------------------------|------------------|

| SC2604MSTRT <sup>(1)(2)</sup> | MSOP-8           |

| SC2604EVB                     | Evaluation Board |

#### Notes:

- (1) Available in tape and reel only. A reel contains 2,500 devices.

- (2) Available in lead-free package only. Device is fully WEEE and RoHS compliant.

# **Marking Information**

# **Absolute Maximum Ratings**

| $V_{_{\mathrm{IN}}}$ Supply Voltage0.3 to 20V |

|-----------------------------------------------|

| CS Pin Voltage0.3 to 20V                      |

| GATE Pin Voltage0.3 to 20V                    |

| DRV Pin Voltage0.3 to 25V                     |

| OCP/EN Pin Voltage0.3 to 7V                   |

| SS/VREF Pin Voltage0.3 to 7V                  |

| FB Pin Voltage0.3 to 7V                       |

| Peak IR Reflow Temperature                    |

| ESD Protection Level <sup>(2)</sup>           |

## **Thermal Information**

| Junction to Ambient (1)             | 160°C/W   |

|-------------------------------------|-----------|

| Junction to Case (1)                | 45°C/W    |

| Maximum Junction Temperature        | 150°C     |

| Storage Temperature -45 to          | to +150°C |

| Lead Temperature (Soldering) 10 sec | 300°C     |

# **Recommended Operating Conditions**

| Input Voltage Range |  | 4.5V to 13.5V |

|---------------------|--|---------------|

|---------------------|--|---------------|

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

- NOTES-

- (1) Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

- (2) Tested according to JEDEC standard JESD22-A114-B.

### Electrical Characteristics \_\_\_\_\_

Unless otherwise noted,  $V_{_{IN}}$  = 12V,  $V_{_{O}}$  = 25V, -40°C <  $T_{_{A}}$  =  $T_{_{J}}$  < 125°C.

| Parameter                        | Conditions                                    | Min   | Тур   | Max   | Units |

|----------------------------------|-----------------------------------------------|-------|-------|-------|-------|

| Input Supply                     |                                               |       |       |       |       |

| V <sub>IN</sub> Supply Voltage   |                                               | 4.5   |       | 13.5  | V     |

| V <sub>IN</sub> Start Voltage    | V <sub>IN</sub> Rising                        |       | 4.2   | 4.5   | V     |

| V <sub>IN</sub> Start Hysteresis |                                               |       | 400   |       | mV    |

| V <sub>IN</sub> Supply Current   | Switching, GATE pin floating                  |       | 6.0   | 9.0   | mA    |

| V <sub>IN</sub> Shutdown Current | OCP/EN = Low                                  |       |       | 200   | μΑ    |

| Error Amplifier                  |                                               | ·     |       |       |       |

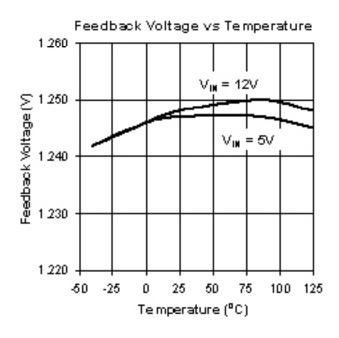

| Feedback Voltage                 | I <sub>o</sub> = 100mA                        | 1.225 | 1.250 | 1.275 | V     |

| Feedback Bias Current            | $V_{IN} = 12V$ , $V_{FB} = V_{SS/VREF}$       |       | 0.5   | 1.0   | μΑ    |

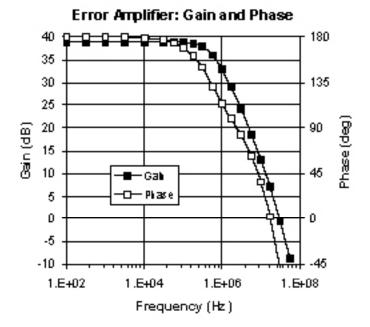

| Error Amplifier Gain (1)         |                                               |       | 90    |       | V/V   |

| Oscillator                       |                                               |       |       |       |       |

| Oscillator Frequency             |                                               | 320   | 400   | 480   | kHz   |

| Maximum Duty Cycle               |                                               | 86    | 90    |       | %     |

| Internal Ramp Peak (2)           |                                               |       | 1.4   |       | V     |

| Internal Ramp Valley (2)         |                                               |       | 0.4   |       | V     |

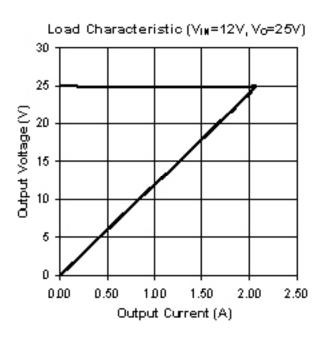

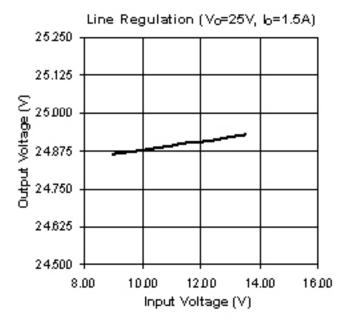

| Regulation                       |                                               |       |       |       |       |

| Load Regulation                  | I <sub>o</sub> = 0.1A to 1A                   |       |       | 0.5   | %     |

| Line Regulation                  | $V_{IN} = 5V \text{ to } 13.5V, I_{O} = 0.1A$ |       |       | 1.0   | %     |

# **Electrical Characteristics (Cont.)**

Unless otherwise noted,  $V_{IN} = 12V$ ,  $V_{O} = 25V$ ,  $-40^{\circ}C < T_{A} = T_{J} < 125^{\circ}C$ .

| Parameter                            | Conditions                                                | Min | Тур | Max | Units |

|--------------------------------------|-----------------------------------------------------------|-----|-----|-----|-------|

| PWM Switch Gate Drive                |                                                           | '   |     | ,   |       |

| Gate Source Current                  | V <sub>IN</sub> = 12V, C <sub>GATE</sub> = 10nF           | 0.5 | 0.8 |     | А     |

| Gate Sink Current                    | V <sub>IN</sub> = 12V, C <sub>GATE</sub> = 10nF           | 0.5 | 0.8 |     | А     |

| PWM Switch Soft Start                |                                                           | ·   |     |     |       |

| Soft Start Charge Current            |                                                           |     | 55  |     | μΑ    |

| SS/VREF Threshold to Shutdown Switch | Pull down below this level to disable PWM Switch gate     |     |     | 100 | mV    |

| SS/VREF Threshold to Turn-on Switch  | Pull above this level to enable PWM Switch gate           | 310 |     |     | mV    |

| Disconnect Switch Gate Drive         |                                                           | '   |     |     |       |

| DRV Source Current                   | $V_{IN} = 12V, V_{DRV} = 15.5V$                           |     | 45  |     | μΑ    |

| DRV Sink Current                     | $V_{IN} = 12V, V_{DRV} = 8V$                              |     | 45  |     | μΑ    |

| Over Current Protection              |                                                           |     |     |     |       |

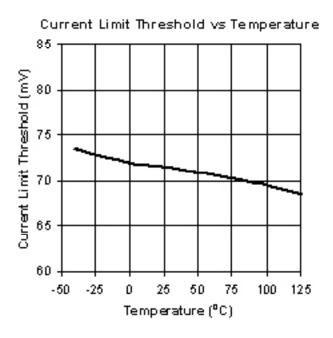

| Current Limit Threshold              | V <sub>IN</sub> - CS                                      | 61  | 72  | 83  | mV    |

| OCP/EN Threshold                     | Pull down below this level to disable Disconnect FET gate | 520 | 590 | 660 | mV    |

| OCP/EN Charge Current                |                                                           |     | 37  |     | μΑ    |

| OCP/EN Discharge Current             |                                                           |     | 1.0 |     | μΑ    |

| CS Input Current                     |                                                           |     | 0.2 |     | μΑ    |

Note: (1). Guaranteed by Characterization

(2). Guaranteed by design

# **Pin Descriptions**

| Pin | Pin Name | Pin Function                                                                                                                                                                                                                                                                     |  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | CS       | Current sense input (negative)                                                                                                                                                                                                                                                   |  |

| 2   | VIN      | Device supply voltage (also positive current sense input)                                                                                                                                                                                                                        |  |

| 3   | GATE     | PWM gate driver output for boost converter                                                                                                                                                                                                                                       |  |

| 4   | GND      | Device ground                                                                                                                                                                                                                                                                    |  |

| 5   | SS/VREF  | Soft start and reference voltage pin                                                                                                                                                                                                                                             |  |

| 6   | FB       | Error amplifier inverted input                                                                                                                                                                                                                                                   |  |

| 7   | OCP/EN   | When a capacitor is tied to this pin, the maximum inrush current is controlled during start-up. The capacitor value also determines the off-time after the device has entered hiccup mode. Pulling this pin low can disable the linear and the switcher to turn off the circuit. |  |

| 8   | DRV      | Gate drive of input disconnect FET limiting system input current                                                                                                                                                                                                                 |  |

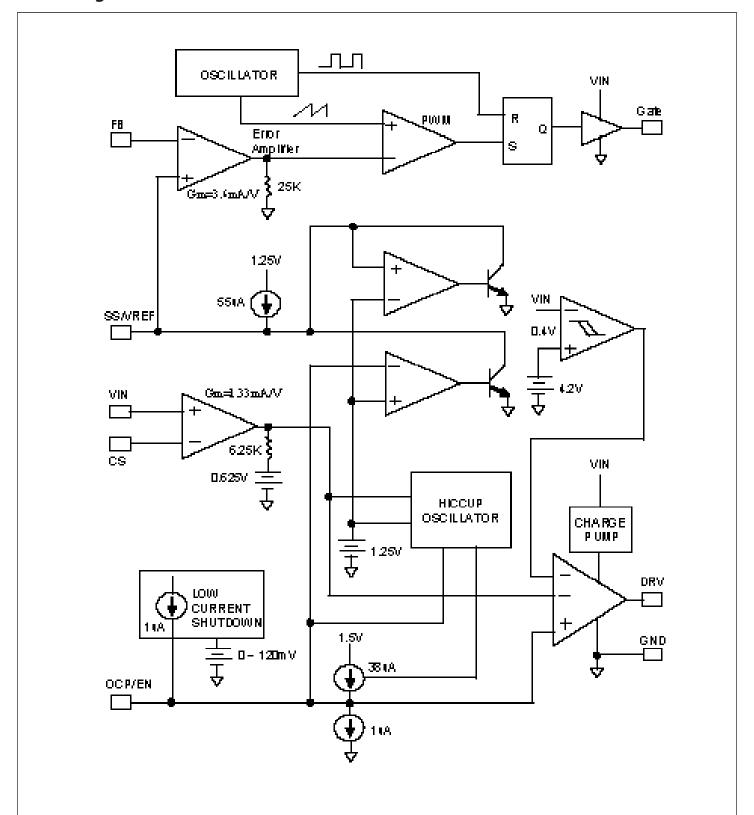

# **Block Diagram**

Figure 2. SC2604 Function Diagram

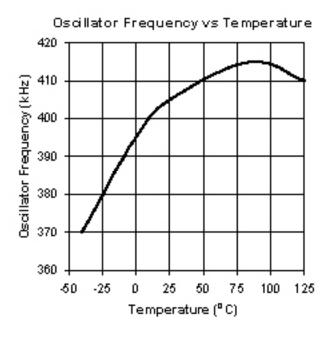

# **Typical Characteristics**

# **Typical Characteristics (Cont.)**

### **Applications Information**

#### **PWM Control Loop**

The SC2604 is a voltage-mode PWM controller with a fixed switching frequency of 400kHz for use in high efficiency, boosted voltage, DC/DC power supplies.

As shown in Figure 2, the PWM control loop of the SC2604 consists of a 400kHz oscillator, a PWM comparator, a voltage error amplifier, and a FET driver. The boost converter output voltage is fed back to FB (error amplifier negative) and is regulated to the reference voltage at SS/VREF pin. The error amplifier output is compared with the 400kHz ramp to generate a PWM wave, which is amplified and used to drive the boost FET ( $Q_2$  in Figure 1) for the converter. The PWM controller works with soft start and fault monitoring circuitry to meet application requirements.

#### **UVLO, Start-up, and Shutdown**

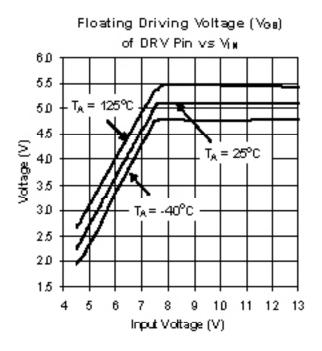

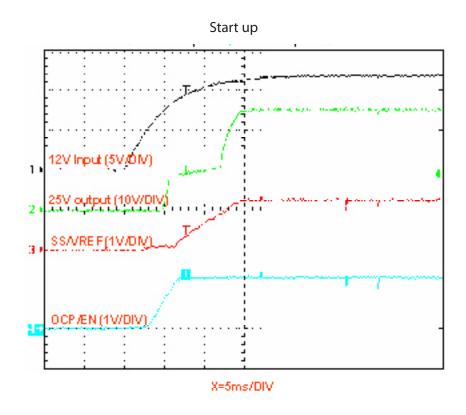

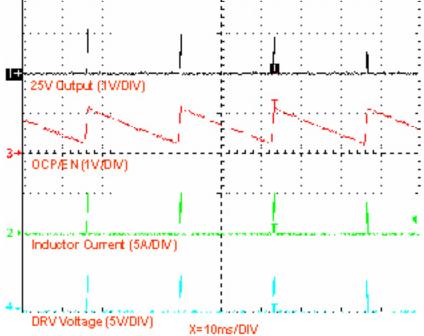

To initiate the SC2604, a supply voltage is applied to  $V_{IN}$ . The DRV and GATE are held low. When V<sub>IN</sub> voltage exceeds UVLO (Under Voltage Lockout) threshold, typically 4.2V, an internal current source (37µA) begins to charge the OCP/EN pin capacitor. The OCP/EN voltage ramps from near ground to over 1.25V but the voltage between 0.625V and 1.25V provides the linear soft-start range for the disconnect FET (Q,). When the OCP/EN voltage is over 1.25V, the OCP hiccup is enabled, and SS/VREF pin is released. At this moment, another internal current source (55µA) begins to charge the SS/VREF pin capacitor. When the SS/VREF pin voltage reaches 0.5V, the error amplifier output will rise to 0.4V, then the PWM comparator begins to switch. The switching regulator output is slowly ramping up for a soft turn-on. The details of SC2604 startup timing is shown in Figure 3.

If the supply voltage at  $V_{IN}$  pin falls below UVLO threshold (3.8V typically) during a normal operation, the DRV pin is pulled low to cut off the supply power of the boost converter, while the OCP/EN pin capacitor is discharged with a 1 $\mu$ A internal current source. When the OCP/EN pin falls below 1.25V, the SS/VREF pin is forced to ground. This completely shuts down the boost conveter.

Directly pulling the OCP/EN pin below 0.52V can also

allow a complete shutdown of the output. Pulling the SS/VREF pin below 0.1V only shuts the boost FET ( $Q_2$  in Figure 1) off and the output voltage will be ( $V_{IN}$ - $V_{rl}$ ).

Figure 3. Start-up Timing Diagram

#### **Hiccup Mode Short Circuit Protection**

Hiccup mode over-current protection is utilized in the SC2604. When an increasing load causes a voltage of 72mv to occur from  $V_{\rm IN}$  to CS then a current limit hiccup sequence is started. The sequence starts by pulling DRV low and discharging the OCP/EN pin with a 1 $\mu$ A current source. When the OCP/EN pin falls below 1.25V, the SS/VREF pin is forced to ground (similar to the UVLO shutdown described in the last setion).

When the voltage on the OCP/EN pin falls to near zero volt, the  $1\mu A$  discharge current becomes a  $37\mu A$  charging current and the OCP/EN pin starts to charge and DRV is enabled. When the OCP/EN voltage rises from 0.625V to 1.25V, the current in the disconnect FET is allowed to increase from zero to a maximum of 72mV/(Current Sense Resistor Value). If the over-current condition still exists when OCP/EN crosses 1.25V then the hiccup sequence will re-start. If there is no over-current as OCP/EN crosses 1.25V then the SS/VREF pin is released to rise and allow a

soft-start of the switching boost regulator.

The DRV pin of the SC2604 is meant to drive an N-Channel FET that can disconnect the input supply in the event of an over-current condition. The OCP/EN capacitor becomes part of a hiccup oscillator that is charged with  $37\mu A$  and discharged with  $1\mu A$  to provide a low duty cycle for the FET  $Q_1$ .

It should be understood that sufficiently fast ramp rates on the OCP/EN pin and the SS/VREF pin can trigger a hiccup event because of the charging current demanded by the boost regulator output capacitor.

#### **Setting the Output Voltage**

In Figure 1, an external resistive divider  $R_7$  and  $R_8$  with its center tap tied to the FB pin sets the output voltage.

$$R_{T} = R_{S} \left( \frac{V_{OUT}}{1.25 V} - 1 \right)$$

In some applications, a RC branch ( $R_{6'}$   $C_{12}$  in the Typical Schematic on page 12) will be needed for loop stability.

#### **Maximum Duty Cycle**

The maximum duty cycle,  $D_{max}$  defines the upper limit of power conversion ratio

$$\frac{V_{QUT}}{V_{M}} = \frac{1}{1 - D_{MAX}}$$

#### **Calculating Current Sense Resistor**

Current sense resistor is placed at the input to sense inductor peak current of the boost regulator. The value of the resistor can be calculated by

$$R_{CS} = \frac{72 \, \text{mV}}{I_{PBAK}}$$

where  $I_{\text{PEAK}}$  is the allowed boost inductor peak current.

In many applications, a noise filter circuit ( $R_1$ =200,  $C_{10}$ =10nF in the Typical Schematic on page 12) may be needed for the input current sensing.

## Capacitor at OCP/EN Pin - C<sub>OCP/EN</sub>

As the current at start-up may hit its current limit threshold, the ramp rate of the current must be slow enough to allow the output capacitor to be fully charged to a voltage one diode drop  $V_d$  less than input voltage  $V_{IN}$ . To guarantee a successful start-up at no load, the value of the capacitor at the OCP/EN pin has to satisfy the following formula:

$$C_{\text{QCP/EM}} > \frac{C_{\text{QUT}} (V_{\text{M}} - V_d)}{0.525} \frac{R_{CS}}{750}$$

#### **Disconnect FET Selection**

The floating driving voltage of DRV pin drops slightly as the supply voltage  $V_{IN}$  is below 7.5V (Typical Characteristics on page 8), where a FET with low gate threshold voltage  $(V_{GS(TH)})$  has to be used for the disconnect FET. In a 5V input application, a FET with  $V_{GS(TH)}$ =2V, such as FDD6672A from Fairchild, is needed.

#### **Layout Guidelines**

Careful attentions to layout requirements are necessary for successful implementation of the SC2604 PWM controller. High currents switching at 400kHz are present in the application and their effect on ground plane voltage differentials must be understood and minimized.

1) The high power parts of the circuit should be laid out first. A ground plane should be used, the number and position of ground plane interruptions should be such as to not unnecessarily compromise ground plane integrity. Isolated or semi-isolated areas of the ground plane may be deliberately introduced to constrain ground currents to particular areas, for example the input capacitor and bottom Schottky ground.

2) The loop formed by the output Capacitor(s) ( $C_{OUT}$ ), the FET ( $Q_1$ ), the current sensing resistor, and the Schottky ( $D_1$ ) must be kept as small as possible, as shown on the layout diagram in Figure 4. This loop contains all the high current, fast transition switching. Connections should be as wide and as short as possible to minimize loop inductance. Minimizing this loop area will reduce EMI,

lower ground injection currents, resulting in electrically "cleaner" grounds for the rest of the system and minimize source ringing, resulting in more reliable gate switching signals.

- 3) The connection between the junction of  $Q_1$ ,  $D_1$  and the output capacitor should be a wide trace or copper region. It should be as short as practical. Since this connection has fast voltage transitions, keeping this connection short will minimize EMI.

- 4) The Output Capacitor(s) ( $C_{\rm OUT}$ ) should be located as close to the load as possible, fast transient load currents are supplied by  $C_{\rm OUT}$  only, and connections between  $C_{\rm OUT}$  and the load must be short, wide copper areas to minimize inductance and resistance.

- 5) The SC2604 is best placed over an isolated ground plane area. The soft-start capacitor and the Vin decoupling capacitor should also connected to this ground pad area. This isolated ground area should be connected to the main ground by a trace that runs from the GND pin to the ground side of the output capacitor. If this is not possible, the GND pin may be connected to the ground path between the Output Capacitor and the  $C_{IN}$ ,  $Q_1$ ,  $D_1$  loop. Under no circumstances should GND be returned to a ground inside the  $C_{IN}$ ,  $Q_1$ ,  $D_1$  loop.

- 6) Input voltage of the SC2604 should be supplied from the power rail through a  $1\Omega$  resistor, the Vin pin should be decoupled directly to GND by a  $0.1\mu F\sim 1\mu F$  ceramic capacitor, trace lengths should be as short as possible.

Note: Heavy lines indicate the critical loop carrying high pulsating current. The inductance of the loop needs to be minimized.

Figure 4. SC2604 Layout Diagram

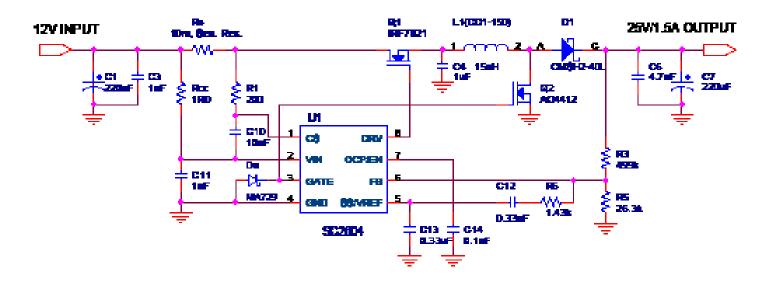

Typical application schematic with 12V input and 25V/1.5A output

Note: A small Schottky diode (Da) may be required in some applications to clamp negative spike at the GATE pin.

#### **Bill of materials**

| Herm | Quantity | Reference | Part (PW of Vender)         | Vendor               |

|------|----------|-----------|-----------------------------|----------------------|

| 1    | 1        | C1        | 220uF/10V                   | Rubyean, ZL          |

| 2    | 3        | C3,C4,C11 | 1uF/16V                     | Vehay                |

| 3    | 1        | CB        | 4.7uF/50V                   | Murata               |

| 4    | 1        | C7        | 220uF/35V/160m              | Rubyean, YXF         |

| 5    | 1        | C10       | 10nF                        | Vishay               |

| 5    | 1        | C12       | 0.33uF                      | Vishay               |

| 7    | 1        | C13       | 0.33uF                      | Vishay               |

| 8    | 1        | C14       | 0.1uF                       | Vehay                |

| 8    | 1        | D1        | CMSH2-40L (Schuttley diode) | Central Semi         |

| 10   | 1        | Da        | MA729 (Schotley diode)      | Parasonic            |

| 11   | 1        | L1        | 15aH/3.5A (CD1-150)         | Californies          |

| 12   | 1        | CH CH     | HR-7821                     | R                    |

| 13   | 1        | Q2        | A01412                      | Alpha & Ornega Semi. |

| 14   | 1        | Rs.       | 15m(Sensing Res.)           | Vishay               |

| 15   | 1        | RH        | 200                         | Vishay               |

| 18   | 1        | Rec       | 1R0                         | Vishay               |

| 17   | 1        | R3        | 499k                        | Vishay               |

| 1B   | 1        | R5        | 2fl_1k                      | Vehay                |

| 1B   | 1        | RB        | 1.43k                       | Vishay               |

| 20   | 1        | UI        | SC2604                      | Semlech              |

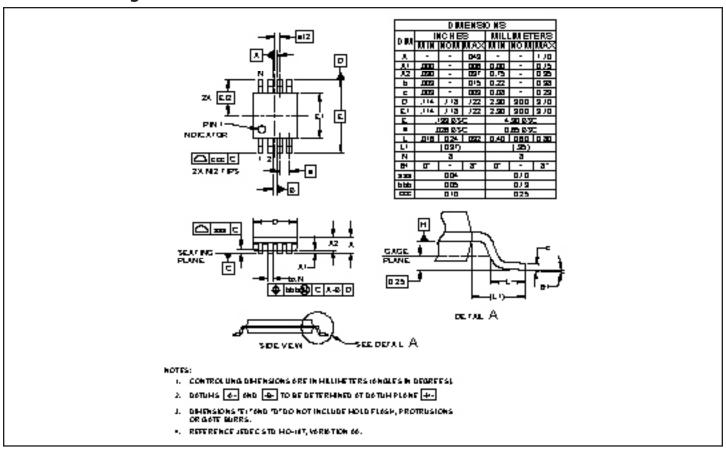

# **Outline Drawing - MSOP-8**

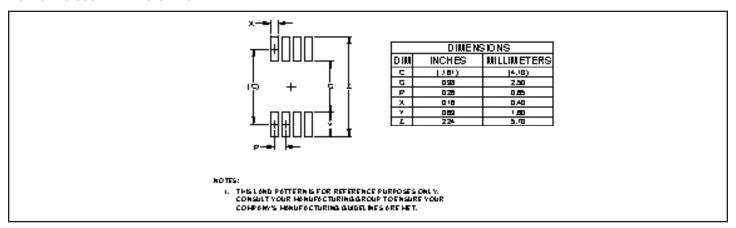

#### **Land Pattern - MSOP-8**

# **Contact Information**

Semtech Corporation

Power Mangement Products Division

200 Flynn Road, Camarillo, CA 93012

Phone: (805) 498-2111 Fax: (805) 498-3804